JEDEC JESD22B113

THE CHALLENGE

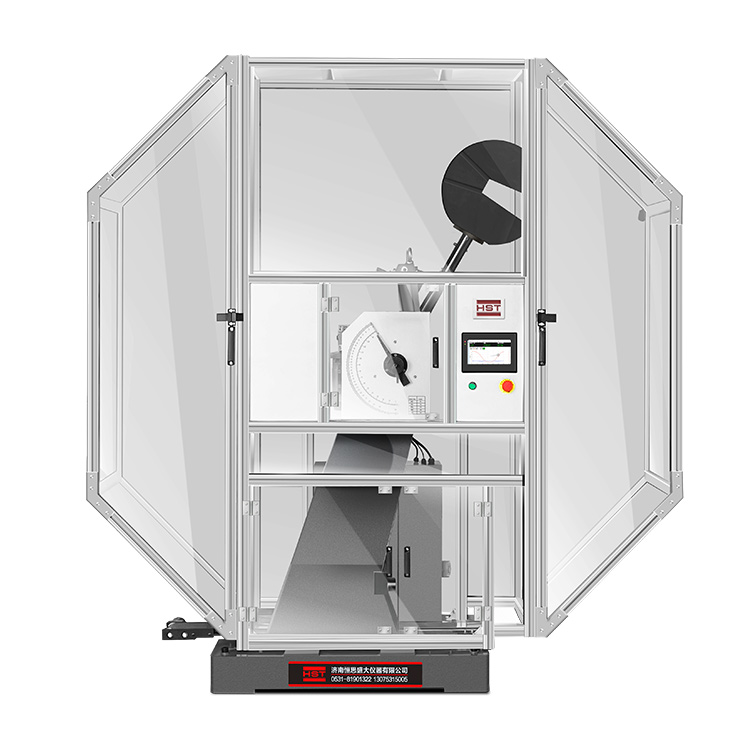

Board Level mechanical tests are an essential quality control test within the microelectronics packaging industry. They provide testing data to support IC components' performance against interconnect failures during shipment and in end-use products where cyclic stresses and shock from impact are experienced.

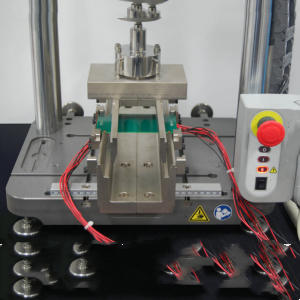

The JEDEC JESD22B113 test method is used to evaluate and compare surface mounted electronic components' performance in an accelerated test environment for handheld electronic products applications. This is done by using a specified 4-point cyclic bending test method.

OUR SOLUTION

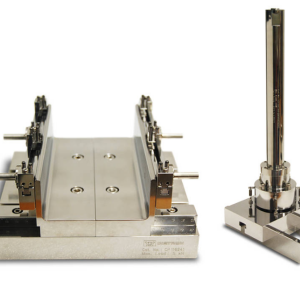

The standard recommends a specimen design similar in size and layout to a drop Impact test. It specifies the spans and the cyclic amplitude, frequency, and waveform for performing this test. Interconnection failure is determined based on resistance daisy chains, typically five times the initial resistance or 1000ohms, whichever is higher. The challenge of the JEDEC JESD22B113 test that an operator must have the test system continuously generate the flexural loading based on a specified cyclic waveform on the printed wiring board (PWB) via the 4-point bend to long-time fatigue – up to 200,000 cycles at 1-3Hz frequency without lateral specimen shifting.